#### **Features**

- Utilizes the AVR<sup>®</sup> Enhanced RISC Architecture

- 89 Powerful Instructions Most Single Clock Cycle Execution

- 1K bytes of In-System Reprogrammable Downloadable Flash

- SPI Serial Interface for Program Downloading

- Endurance: 1,000 Write/Erase Cycles

- 64 bytes EEPROM

- Endurance: 100,000 Write/Erase Cycles

- 32 x 8 General Purpose Working Registers

- 15 Programmable I/O Lines

- V<sub>CC</sub>: 2.7 6.0V

- Fully Static Operation, 0 16 MHz

- Instruction Cycle Time: 62.5 ns @ 16 MHz

- One 8-Bit Timer/Counter with Separate Prescaler

- External and Internal Interrupt Sources

- Programmable Watchdog Timer with On-Chip Oscillator

- On-Chip Analog Comparator

- Low Power Idle and Power Down Modes

- Programming Lock for Software Security

- 20-Pin Device

- Selectable On-Chip RC Oscillator for Zero External Components

#### **Description**

The AT90S1200 is a low-power CMOS 8-bit microcontroller based on the AVR® enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the AT90S1200 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

The AVR core combines a rich instruction set with the 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

(continued)

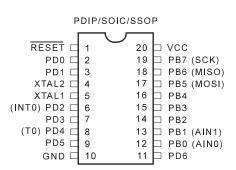

### **Pin Configuration**

8-Bit AVR®

Microcontroller

with 1K bytes

Downloadable

Flash

AT90S1200

### **Block Diagram**

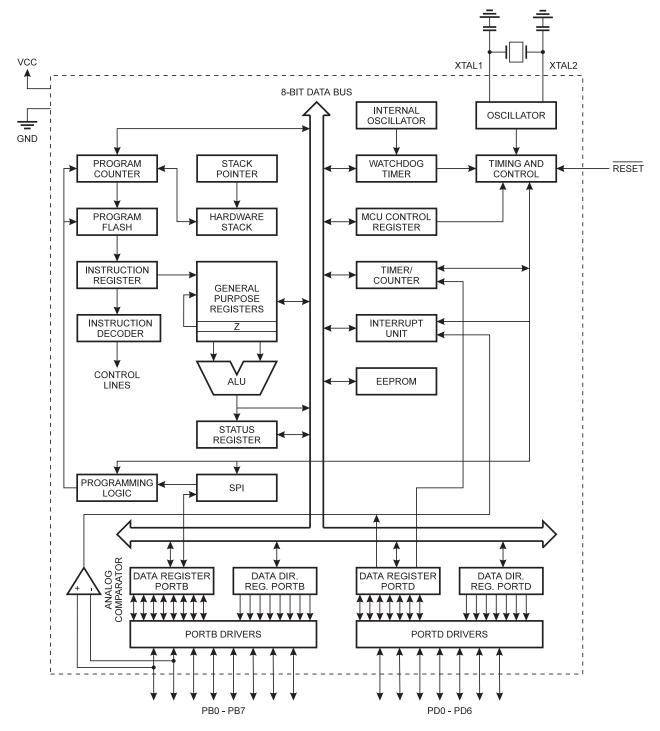

Figure 1. The AT90S1200 Block Diagram

#### **Description (Continued)**

The architecture supports extremely dense assembler code programs. The AT90S1200 provides the following features: 1K bytes of downloadable Flash, 64 bytes EEPROM, 15 general purpose I/O lines, 32 general purpose working registers, internal and external interrupts, programmable watchdog timer with internal oscillator, an SPI serial port for program downloading and two software selectable power saving modes. The idle mode stops the CPU while allowing the registers, timer/counter, watchdog and interrupt system to continue functioning. The power down mode saves the register contents but freezes the oscillator, disabling all other chip functions until the next external interrupt or hardware reset.

The device is manufactured using Atmel's high density non-volatile memory technology. The on-chip downloadable Flash allows the program memory to be reprogrammed in-system through an SPI serial interface or by a conventional nonvolatile memory programmer. By combining an enhanced RISC 8-bit CPU with downloadable Flash on a monolithic chip, the Atmel AT90S1200 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

The AT90S1200 *AVR* is supported with a full suite of program and system development tools including: macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits.

#### **On-Chip RC Oscillator**

An on-chip RC oscillator running at a fixed frequency of 1 MHz can be selected as the MCU clock source. If enabled, the AT90S1200 can operate with no external components. A control bit - RCEN in the Flash Memory selects the on-chip RC oscillator as the clock source when programmed ('0').

#### **Architectural Overview**

The fast-access register file contains 32 x 8-bit general purpose working registers with a single clock cycle access time. This means that during one single clock cycle, one ALU (Arithmetic Logic Unit) operation is executed. Two operands are output from the register file, the operation is executed, and the result is stored back in the register file - in one clock cycle.

The ALU supports arithmetic and logic functions between registers or between a constant and a register. Single register operations are also executed in the ALU. The *AVR* is a Harvard architecture - with separate memories and buses for program and data memories. The program memory is accessed with single level pipelining. While one instruction is being executed, the next instruction is pre-fetched from the program memory. This concept enables instructions to be executed in every clock cycle. The program memory is in-system downloadable Flash memory.

With the relative jump and relative call instructions, the whole 1K byte address space is directly accessed. All AT90S1200 instructions have a single 16-bit word format, meaning that every program memory address contains a single 16-bit instruction.

During interrupts and subroutine calls, the return address program counter (PC) is stored on the stack. The stack is a 3 level deep hardware stack dedicated for subroutines and interrupts.

The I/O memory space contains 64 addresses for CPU peripheral functions as Control Registers, Timer/Counters, A/D-converters, and other I/O functions. The memory spaces in the AVR architecture are all linear and regular memory maps.

A flexible interrupt module has its control registers in the I/O space with an additional global interrupt enable bit in the status register. Each interrupt has a separate interrupt vector in the interrupt vector table at the beginning of the program memory. Interrupts have priority in accordance with their interrupt vector position. The lower the interrupt address vector the higher priority.

# AT90S1200 Register Summary

| Address      | Name              | Bit 7     | Bit 6         | Bit 5         | Bit 4    | Bit 3  | Bit 2  | Bit 1  | Bit 0    | Page |

|--------------|-------------------|-----------|---------------|---------------|----------|--------|--------|--------|----------|------|

| \$3F         | SREG              |           | Т             | Н             | S        | V      | N      | Z      | С        | 12   |

| \$3E         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$3D         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$3C         | Reserved          |           | I             | I             | I        | 1      | 1      | I      | I        |      |

| \$3B         | GIMSK             | -         | INT0          | -             | -        | -      | -      | -      | -        | 17   |

| \$3A<br>\$39 | Reserved<br>TIMSK | _         | _             | _             | _        | _      | _      | TOIE0  | _        | 18   |

| \$38         | TIFR              | -         | -             | -             | -        | -      | -      | TOV0   | -        | 18   |

| \$37         | Reserved          | _         | <u> </u>      | ļ             | <u> </u> | !      |        | 1000   | <u> </u> | 10   |

| \$36         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$35         | MCUCR             | -         | -             | SE            | SM       | -      | -      | ISC01  | ISC00    | 19   |

| \$34         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$33         | TCCR0             | -         | -             | -             | -        | -      | CS02   | CS01   | CS00     | 21   |

| \$32         | TCNT0             | Timer/Cou | nter0 (8 Bit) |               |          |        |        |        |          | 22   |

| \$31         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$30         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$2F         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$2E         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$2D         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$2C         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$2B         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$2A         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$29         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$28         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$27         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$26         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$25         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$24         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$23         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$22<br>\$21 | Reserved<br>WDTCR |           | _             | _             | _        | WDE    | WDP2   | WDP1   | WDP0     | 23   |

| \$20         | Reserved          | -         | -             | -             | -        | I WDE  | WDFZ   | I WDF1 | VVDPU    | 23   |

| \$1F         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$1E         | EEAR              | _         | FEPROM A      | ddress Regist | or       |        |        |        |          | 24   |

| \$1D         | EEDR              | FEPROM    | Data Register |               | .01      |        |        |        |          | 24   |

| \$1C         | EECR              | -         | -             | _             | _        | _      | _      | EEWE   | EERE     | 24   |

| \$1B         | Reserved          |           |               |               |          | •      |        |        |          |      |

| \$1A         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$19         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$18         | PORTB             | PORTB7    | PORTB6        | PORTB5        | PORTB4   | PORTB3 | PORTB2 | PORTB1 | PORTB0   | 26   |

| \$17         | DDRB              | DDB7      | DDB6          | DDB5          | DDB4     | DDB3   | DDB2   | DDB1   | DDB0     | 27   |

| \$16         | PINB              | PINB7     | PINB6         | PINB5         | PINB4    | PINB3  | PINB2  | PINB1  | PINB0    | 27   |

| \$15         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$14         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$13         | Reserved          |           |               | 1             |          | •      | ı      |        |          |      |

| \$12         | PORTD             | -         | PORTD6        | PORTD5        | PORTD4   | PORTD3 | PORTD2 | PORTD1 | PORTD0   | 31   |

| \$11         | DDRD              | -         | DDD6          | DDD5          | DDD4     | DDD3   | DDD2   | DDD1   | DDD0     | 31   |

| \$10         | PIND              | -         | PIND6         | PIND5         | PIND4    | PIND3  | PIND2  | PIND1  | PIND0    | 31   |

| \$0F         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$0E         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$0D         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$0C         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$0B         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$0A         | Reserved          |           |               |               |          |        |        |        |          |      |

| \$09<br>\$08 | Reserved          | ACD       |               | 100           | ۸۵۱      | ACIE   |        | ACIC4  | ACICO    | OF.  |

| \$08         | ACSR<br>Reserved  | ACD       | -             | ACO           | ACI      | ACIE   | -      | ACIS1  | ACIS0    | 25   |

|              | i Keservea        |           |               |               |          |        |        |        |          |      |

## AT90S1200 Instruction Set Summary

| Mnemonic            | Operands      | Description                            | Operation                                             | Flags      | #Clocks |

|---------------------|---------------|----------------------------------------|-------------------------------------------------------|------------|---------|

| ARITHMETIC A        | ND LOGIC INST | RUCTIONS                               | ·                                                     | , -        |         |

| ADD                 | Rd, Rr        | Add two Registers                      | $Rd \leftarrow Rd + Rr$                               | Z,C,N,V,H  | 1       |

| ADC                 | Rd, Rr        | Add with Carry two Registers           | $Rd \leftarrow Rd + Rr + C$                           | Z,C,N,V,H  | 1       |

| SUB                 | Rd, Rr        | Subtract two Registers                 | Rd ← Rd - Rr                                          | Z,C,N,V,H  | 1       |

| SUBI                | Rd, K         | Subtract Constant from Register        | Rd ← Rd - K                                           | Z,C,N,V,H  | 1       |

| SBC                 | Rd, Rr        | Subtract with Carry two Registers      | Rd ← Rd - Rr - C                                      | Z,C,N,V,H  | 1       |

| SBCI                | Rd, K         | Subtract with Carry Constant from Reg. | Rd ← Rd - K - C                                       | Z,C,N,V,H  | 1       |

| AND                 | Rd, Rr        | Logical AND Registers                  | Rd ← Rd • Rr                                          | Z,N,V      | 1       |

| ANDI                | Rd, K         | Logical AND Register and Constant      | Rd ← Rd • K                                           | Z,N,V      | 1       |

| OR                  | Rd, Rr        | Logical OR Registers                   | Rd ← Rd v Rr                                          | Z,N,V      | 1       |

| ORI                 | Rd, K         | Logical OR Register and Constant       | $Rd \leftarrow Rd \vee K$                             | Z,N,V      | 1       |

| EOR                 | Rd, Rr        | Exclusive OR Registers                 | Rd ← Rd⊕Rr                                            | Z,N,V      | 1       |

| COM                 | Rd            | One's Complement                       | Rd ← \$FF - Rd                                        | Z,C,N,V    | 1       |

| NEG                 | Rd            | Two's Complement                       | Rd ← \$00 - Rd                                        | Z,C,N,V,H  | 1       |

| SBR                 | Rd,K          | Set Bit(s) in Register                 | Rd ← Rd v K                                           | Z,N,V      | 1       |

| CBR                 | Rd,K          | Clear Bit(s) in Register               | $Rd \leftarrow Rd \bullet (FFh - K)$                  | Z,N,V      | 1       |

| INC                 | Rd            | Increment                              | Rd ← Rd + 1                                           | Z,N,V      | 1       |

| DEC                 | Rd            | Decrement                              | Rd ← Rd - 1                                           | Z,N,V      | 1       |

| TST                 | Rd            | Test for Zero or Minus                 | $Rd \leftarrow Rd \bullet Rd$                         | Z,N,V      | 1       |

| CLR                 | Rd            | Clear Register                         | Rd ← Rd⊕Rd                                            | Z,N,V      | 1       |

| SER                 | Rd            | Set Register                           | Rd ← \$FF                                             | None       | 1       |

| <b>BRANCH INSTR</b> | RUCTIONS      |                                        |                                                       |            |         |

| RJMP                | k             | Relative Jump                          | PC ← PC + k + 1                                       | None       | 2       |

| RCALL               | k             | Relative Subroutine Call               | PC ← PC + k + 1                                       | None       | 3       |

| RET                 |               | Subroutine Return                      | PC ← STACK                                            | None       | 4       |

| RETI                |               | Interrupt Return                       | PC ← STACK                                            | 1          | 4       |

| CPSE                | Rd,Rr         | Compare, Skip if Equal                 | if $(Rd = Rr) PC \leftarrow PC + 2 \text{ or } 3$     | None       | 1/2     |

| СР                  | Rd,Rr         | Compare                                | Rd - Rr                                               | Z, N,V,C,H | 1       |

| CPC                 | Rd,Rr         | Compare with Carry                     | Rd - Rr - C                                           | Z, N,V,C,H | 1       |

| CPI                 | Rd,K          | Compare Register with Immediate        | Rd - K                                                | Z, N,V,C,H | 1       |

| SBRC                | Rr, b         | Skip if Bit in Register Cleared        | if (Rr(b)=0) PC ← PC + 2 or 3                         | None       | 1/2     |

| SBRS                | Rr, b         | Skip if Bit in Register is Set         | if $(Rr(b)=1) PC \leftarrow PC + 2 \text{ or } 3$     | None       | 1/2     |

| SBIC                | P, b          | Skip if Bit in I/O Register Cleared    | if (P(b)=0) PC ← PC + 2 or 3                          | None       | 1/2     |

| SBIS                | P, b          | Skip if Bit in I/O Register is Set     | if (P(b)=1) PC ← PC + 2 or 3                          | None       | 1/2     |

| BRBS                | s, k          | Branch if Status Flag Set              | if $(SREG(s) = 1)$ then $PC \leftarrow PC + k + 1$    | None       | 1/2     |

| BRBC                | s, k          | Branch if Status Flag Cleared          | if $(SREG(s) = 0)$ then $PC \leftarrow PC + k + 1$    | None       | 1/2     |

| BREQ                | k             | Branch if Equal                        | if $(Z = 1)$ then $PC \leftarrow PC + k + 1$          | None       | 1/2     |

| BRNE                | k             | Branch if Not Equal                    | if $(Z = 0)$ then $PC \leftarrow PC + k + 1$          | None       | 1/2     |

| BRCS                | k             | Branch if Carry Set                    | if (C = 1) then PC $\leftarrow$ PC + k + 1            | None       | 1/2     |

| BRCC                | k             | Branch if Carry Cleared                | if (C = 0) then PC ← PC + k + 1                       | None       | 1/2     |

| BRSH                | k             | Branch if Same or Higher               | if (C = 0) then PC ← PC + k + 1                       | None       | 1/2     |

| BRLO                | k             | Branch if Lower                        | if (C = 1) then PC $\leftarrow$ PC + k + 1            | None       | 1/2     |

| BRMI                | k             | Branch if Minus                        | if (N = 1) then PC ← PC + k + 1                       | None       | 1/2     |

| BRPL                | k             | Branch if Plus                         | if $(N = 0)$ then $PC \leftarrow PC + k + 1$          | None       | 1/2     |

| BRGE                | k             | Branch if Greater or Equal, Signed     | if $(N \oplus V = 0)$ then $PC \leftarrow PC + k + 1$ | None       | 1/2     |

| BRLT                | k             | Branch if Less Than Zero, Signed       | if $(N \oplus V = 1)$ then $PC \leftarrow PC + k + 1$ | None       | 1/2     |

| BRHS                | k             | Branch if Half Carry Flag Set          | if (H = 1) then PC ← PC + k + 1                       | None       | 1/2     |

| BRHC                | k             | Branch if Half Carry Flag Cleared      | if (H = 0) then PC ← PC + k + 1                       | None       | 1/2     |

| BRTS                | k             | Branch if T Flag Set                   | if $(T = 1)$ then $PC \leftarrow PC + k + 1$          | None       | 1/2     |

| BRTC                | k             | Branch if T Flag Cleared               | if (T = 0) then PC ← PC + k + 1                       | None       | 1/2     |

| BRVS                | k             | Branch if Overflow Flag is Set         | if (V = 1) then PC ← PC + k + 1                       | None       | 1/2     |

| BRVC                | k             | Branch if Overflow Flag is Cleared     | if (V = 0) then PC ← PC + k + 1                       | None       | 1/2     |

| BRIE                | k             | Branch if Interrupt Enabled            | if ( I = 1) then PC ← PC + k + 1                      | None       | 1/2     |

| BRID                | k             | Branch if Interrupt Disabled           | if ( I = 0) then PC ← PC + k + 1                      | None       | 1/2     |

(continued)

## AT90S1200 Instruction Set Summary (Continued)

| Mnemonic           | Operands     | Description                    | Operation                                                     | Flags   | #Clocks |

|--------------------|--------------|--------------------------------|---------------------------------------------------------------|---------|---------|

| DATA TRANSFER II   | NSTRUCTIONS  |                                |                                                               |         |         |

| LD                 | Rd,Z         | Load Register Indirect         | $Rd \leftarrow (Z)$                                           | None    | 2       |

| ST                 | Z,Rr         | Store Register Indirect        | (Z) ← Rr                                                      | None    | 2       |

| MOV                | Rd, Rr       | Move Between Registers         | Rd ← Rr                                                       | None    | 1       |

| LDI                | Rd, K        | Load Immediate                 | Rd ← K                                                        | None    | 1       |

| IN                 | Rd, P        | In Port                        | Rd ← P                                                        | None    | 1       |

| OUT                | P, Rr        | Out Port                       | P ← Rr                                                        | None    | 1       |

| BIT AND BIT-TEST I | INSTRUCTIONS |                                | <u> </u>                                                      | •       | -       |

| SBI                | P,b          | Set Bit in I/O Register        | I/O(P,b) ← 1                                                  | None    | 2       |

| CBI                | P,b          | Clear Bit in I/O Register      | I/O(P,b) ← 0                                                  | None    | 2       |

| LSL                | Rd           | Logical Shift Left             | $Rd(n+1) \leftarrow Rd(n), Rd(0) \leftarrow 0$                | Z,C,N,V | 1       |

| LSR                | Rd           | Logical Shift Right            | $Rd(n) \leftarrow Rd(n+1), Rd(7) \leftarrow 0$                | Z,C,N,V | 1       |

| ROL                | Rd           | Rotate Left Through Carry      | $Rd(0)\leftarrow C,Rd(n+1)\leftarrow Rd(n),C\leftarrow Rd(7)$ | Z,C,N,V | 1       |

| ROR                | Rd           | Rotate Right Through Carry     | $Rd(7)\leftarrow C,Rd(n)\leftarrow Rd(n+1),C\leftarrow Rd(0)$ | Z,C,N,V | 1       |

| ASR                | Rd           | Arithmetic Shift Right         | $Rd(n) \leftarrow Rd(n+1), n=06$                              | Z,C,N,V | 1       |

| SWAP               | Rd           | Swap Nibbles                   | $Rd(30) \leftarrow Rd(74), Rd(74) \leftarrow Rd(30)$          | None    | 1       |

| BSET               | s            | Flag Set                       | SREG(s) ← 1                                                   | SREG(s) | 1       |

| BCLR               | S            | Flag Clear                     | $SREG(s) \leftarrow 0$                                        | SREG(s) | 1       |

| BST                | Rr, b        | Bit Store from Register to T   | $T \leftarrow Rr(b)$                                          | Т       | 1       |

| BLD                | Rd, b        | Bit load from T to Register    | $Rd(b) \leftarrow T$                                          | None    | 1       |

| SEC                |              | Set Carry                      | C ← 1                                                         | С       | 1       |

| CLC                |              | Clear Carry                    | C ← 0                                                         | С       | 1       |

| SEN                |              | Set Negative Flag              | N ← 1                                                         | N       | 1       |

| CLN                |              | Clear Negative Flag            | N ← 0                                                         | N       | 1       |

| SEZ                |              | Set Zero Flag                  | Z ← 1                                                         | Z       | 1       |

| CLZ                |              | Clear Zero Flag                | Z ← 0                                                         | Z       | 1       |

| SEI                |              | Global Interrupt Enable        | I ← 1                                                         | 1       | 1       |

| CLI                |              | Global Interrupt Disable       | 1 ← 0                                                         | 1       | 1       |

| SES                |              | Set Signed Test Flag           | S ← 1                                                         | S       | 1       |

| CLS                |              | Clear Signed Test Flag         | S ← 0                                                         | S       | 1       |

| SEV                |              | Set Twos Complement Overflow   | V ← 1                                                         | V       | 1       |

| CLV                |              | Clear Twos Complement Overflow | V ← 0                                                         | V       | 1       |

| SET                |              | Set T in SREG                  | T ← 1                                                         | Т       | 1       |

| CLT                |              | Clear T in SREG                | T ← 0                                                         | Т       | 1       |

| SEH                |              | Set Half Carry Flag in SREG    | H ← 1                                                         | Н       | 1       |

| CLH                |              | Clear Half Carry Flag in SREG  | H ← 0                                                         | Н       | 1       |

| NOP                |              | No Operation                   |                                                               | None    | 1       |

| SLEEP              |              | Sleep                          | (see specific descr. for Sleep function)                      | None    | 3       |

| WDR                |              | Watch Dog Reset                | (see specific descr. for WDR/timer)                           | None    | 1       |